儅僀僾儘僕僃僋僩倃丂乽傂傒偮俁乿

丂傂傒偮俀傕傑偩偱偒偰偄側偄偺偵丄傂傒偮俁偭偰丄側傫側傫偩偐丅庯枴偩偐傜丄媊柋傕擺婜傕側偔偄偄壛尭側傕偺偩乮徫乯丅

壗傪傗偭偰偄傞偐偲偄偆偲丄侽侽俁俁偺懕偒傒偨偄側傕偺偱丄價僨僆僗乕僷乕僀儞億乕僘傪尋媶偟偰偄傞丅

丂僗乕僷乕僀儞億乕僘偺尨棟偼丄偳偙偐偵彂偄偨偐傕偟傟側偄偑丄摨婜怣崋傪婎弨偵偟偰暥帤偺昞帵埵抲傪寛傔偰偄傞丅

偦偟偰丄偦偺昞帵僞僀儈儞僌偑偒偨傜丄塮憸怣崋傪愗傝姺偊偰丄僉儍儔僋僞僕僃僱儗乕僞偐傜偺怣崋傪憓擖偡傞傢偗偩丅偙傟偱

尦偺塮憸偵暥帤傪廳偹崌傢偣傞丅

丂傕偟摨婜怣崋偵捛廬偱偒側偐偭偨傜丄暥帤偑曵傟傞偙偲偼尵偆傑偱傕側偄丅悈暯曽岦偑摿偵栤戣偵側傞丅傑偢偼丄偙傟偱

崲偭偨宱尡傪榖偦偆丅

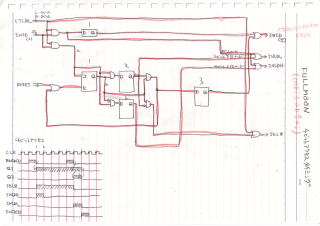

丂怣崋尮偲偟偰丄埲慜嶌偭偨廐寧揹巕偺乽俶俿俽俠僇儔乕僷僞乕儞僕僃僱儗乕僞僉僢僩乿傪巊偭偰偄偨丅價僨僆傗僥儗價偑怣崋尮

偩偭偨傜塮憸偑摦偄偰應掕偟偯傜偄偐傜丄昁慠揑偵偙傟傪巊偭偰偄偨丅偩偑丄偙傟偑僩儔僽儖偺尨場偵側傞偲偼丄嵟弶傑偭偨偔

峫偊傕偟側偐偭偨丅

丂僗乕僷乕僀儞億乕僘夞楬偼丄傾儖僥儔偺儘僕僢僋偱慻傫偩丅摨婜怣崋傪係儊僈偱僒儞僾儕儞僌偟丄棫偪忋偑傝傪専弌偟偨傜

僇僂儞僞傪夞偟偰丄昞帵僞僀儈儞僌傪偲傞曽幃偩丅僨僕僞儖揑側抶墑夞楬偲偄偆傢偗丅壏搙曄壔傗揹埑曄壔偵懳偟偰傕埨掕

偟偰偄傞丅

丂傛偆傗偔暥帤偑昞帵偱偒傞偖傜偄偺夞楬偑偱偒偨偺偱丄僥僗僩偟偰傒偨丅偡傞偲丄悈暯曽岦偑僊僓僊僓偵側偭偰偟傑偭偨丅

側傫偱偩傠偆丅僀儞僞乕儗乕僗偺娭學偐丠偄傗堘偭偨丅係儊僈偱僒儞僾儕儞僌偟偰偄傞偐傜偐丠偦傟偱傕側偄傛偆偩丅側偤偩

傠偆丠

丂摨婜怣崋偭偰丄偦傫側偵傆傜偮偔傕偺偩傠偆偐丅偦傟偲傕摨婜暘棧夞楬偵壗偐栤戣偑偁偭偰丄晄埨掕側偺偐丅偄傠偄傠

媈偭偰挷傋偨偑丄栤戣側偄傛偆偩偭偨丅

丂偄傠偄傠帋偟偨偑慡偔夵慞偟側偄丅壗偑埆偄偺偐偝偭傁傝傢偐傜側偄丅崲偭偨崲偭偨丅偱傕偄偮傑偱傕懌摜傒偟偰偄偨傜

暔偑偱偒側偄丅偲傝偁偊偢懠偺晹暘偺愝寁偵堏偭偨丅

丂側傫偩偐傫偩偱俀儢寧偖傜偄宱夁偟偨偩傠偆偐丒丒丒夞楬婯柾偐傜峫偊偰丄傾儖僥儔俀屄偵暘妱偡傞偙偲偵側傝丄戝婯柾側

愝寁曄峏傪偟偨丅偦偺俀屄偺偆偪偺侾屄偑價僨僆廃曈偺夞楬偱丄傑偢偼栚偵尒偊傞晹暘偐傜嶌傝丄妋幚偵摦嶌偝偣偰偄偙偆

偲偟偰偄偨丅

丂嵞傃昞帵夞楬偑摦偐偣傞忬懺偵側偭偨偺偱丄崱搙偼僒儞僾儕儞僌偑侾俇儊僈偩偟丄埲慜傛傝偼岆嵎偑彮側偔側傞偵堘偄

側偄偲婜懸偟偰揹尮傪擖傟偨偺偩偑丒丒丒偁傝傖丠傗偭傁傝悈暯僈僒僈僒偩両両側傫偱両両両両

丂偙偆側傞偲壗偑埆偄偺偐僒僢僷儕偱偁傞丅

丂偱傕壗偐偟傜傾僋僔儑儞傪婲偙偟偰傒傛偆丅壗偐曄壔偑偁偭偨傜丄巺岥偑偮偐傔傞偐傕偟傟側偄丅偦偆巚偭偰丄傑偢偼塮憸怣崋

尮傪丄價僨僆偵偟偰傒偨丅

丂偡傞偲両僈僒僈僒偑柧傜偐偵彫偝偔側偭偨丅壗偑堘偆傫偩傠偆丠偙偺價僨僆偩偗偺栤戣偐偲巚偭偰丄傓偐偟嶌偭偨乮侽侽俁俁乯

僨傿僗僾儗僀僐儞僩儘乕儔偵偮側偓偐偊偰傒偨丅偮傑傝摨婜怣崋敪惗婍偺戙梡偩丅寢壥偼丄偝傜偵僈僒僈僒偑尭偭偰丄栚棫偨側偄

偖傜偄偵側偭偨丅

丂偙偙偱廐寧揹巕偺乽俶俿俽俠僇儔乕僷僞乕儞僕僃僱儗乕僞僉僢僩乿偺愢柧彂傪傂偭傁傝偩偟偰丄挱傔偰傒偨丅昞巻偵偼乽僾儘偺

巇條乮巊梡偺岆傝偐丠乯偵傕廫暘懴偊傜傟傞傛偆俶俿俽俠婯奿傪戞堦偵愝寁偟偰偄傑偡丅乿側傫偰彂偄偰偁傞丅

丂側偵偭丄僟儊偠傖傫両両

丂偙偺僉僢僩偼丄俙俲俬亅俉侽儅僀僐儞儃乕僪偵傛偭偰乮僜僼僩偱乯塮憸怣崋傪嶌傝弌偟偰偄傞偑丄偙偙偵栤戣偑偁傞丅僜僼僩偺

尷奅偑偦偙偵偁偭偨丅媡傾僙儞僽儖偟偰偄側偄偺偱丄尰抜奒偱偼偁偔傑偱傕悇應偺堟傪弌側偄偺偱偁傞偑丄偍偦傜偔丄

妱傝崬傒偺僞僀儈儞僌偺旝柇側僘儗偐丄僾儘僌儔儉偺棳傟揑側傕偺偱幚峴帪娫偑曄摦偡傞偨傔丄悈暯摨婜偑旝柇偵曄摦偟偰

偄傞偲巚偆丅偩偐傜丄悈暯偺僈僒僈僒偑栚棫偮偺偩丅

丂僀僇儞両丂僾儘側偺偵乮帺徧丠乯丄偙傫側傾儅僠儏傾側怣崋尮偵棅偭偰奐敪傪恑傔偰偄偨側傫偰丒丒丒丅寁應婍椶偼丄婎弨偩偐傜

帺嶌偼偟側偄偱丄怣梡偱偒傞巗斕昳傪慖傏偆偲偄偆億儕僔乕偱傗偭偰偒偨偼偢側偺偵丄側偵儅僰働側帠傗偭偰傫偩乮徫乯丅

丂偦傫側傢偗偱丄摉暘偼怺栭偐憗挬偺僥僗僩僷僞乕儞傪棅傝偵偟偰乮徫乯丄挷惍傪恑傔偰偄偔偙偲偵側傞偩傠偆丅偄偢傟丄拞屆偱傕

椙偄偐傜丄偪傖傫偲偟偨僷僞乕儞僕僃僱儗乕僞傪攦偍偆丅

丂偙偺廐寧僉僢僩偼丄僜僼僩偱塮憸怣崋傪嶌偭偰偄傞埲忋丄尷奅偑偁傞偟抳柦揑側寚娮偩偲巚偆丅摨婜怣崋敪惗偼丄愱梡俬俠傪

巊偆傋偒偩偲巚偆丅偦偆偡傟偽摨婜怣崋偺岆嵎偼丒丒丒偄傗丄昞帵僷僞乕儞偲偐傕怱攝偵側偭偰偒偨側偁丅偙偺嵺丄慡晹僴乕僪

僂僃傾偱嶌偭偰偟傑偆偐丠

丂側偍廐寧僉僢僩偺愢柧彂偵偼丄乽倖倧倰丂俹倰倧倖倕倱倱倝倧値倎倢丂愱栧媄弍幰偺傒側偝傑傊乿偲偄偆崁栚偑偁偭偨偑丄塮憸怣崋儗儀儖偲偐

偺婰弎偽偐傝偱丄摨婜怣崋偵偮偄偰偼慡偔傆傟傜傟偰偄側偐偭偨丅

仠屻擔婰

丂廐寧僉僢僩偺栤戣偠傖側偄傛偆偩丅傗偭傁傝帺暘偺夞楬偵壗傜偐偺栤戣偑丒丒丒丅乮偛傔傫廐寧偝傫乯

丂尨場偼偄偔偮偐廳側偭偰偄偰丄傂偲偮偼僲僀僘偩偭偨丅僲僀僘偺偣偄偱摨婜専弌偺儗儀儖偑嫸偭偰丄悈暯僞僀儈儞僌偑僈僒僈僒

偵側偭偰偄偨丅偦傟偐傜丄僇儔乕僶乕僗僩偑摨婜暘棧偵塭嬁偟偰偄傞傛偆偱丄僼傿儖僞乕偺掕悢傪尒捈偡昁梫桳傝偩丅偝傜偵丄

婎杮揑側栤戣偑偁傞偗偳偙傟偼夝庍偟偩偄偱夝寛偟偦偆丅

丂幨恀偑彫偝偄偑丄偙偺婘忋偺婎斅傜偟偒暔偑尰忬偺帋嶌婡丅攝慄偑僋僔儍僋僔儍丅僨僕僞儖晹偼儐僯僶乕僒儖婎斅俬俠俛亅俆侽係偑

俀奒寶偰偱丄傾僫儘僌晹偼戝侾枃丄彫俀枃偺峔惉丅

仠偦偺屻

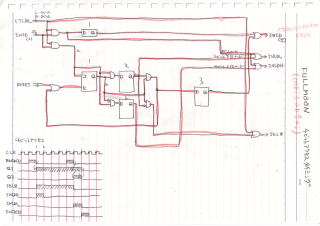

丂偦傠偦傠姰惉堦曕庤慜偲偄偭偨偲偙傠偱偡偑丄傂偨偡傜乽幏擮乿偲乽崻惈乿偱偁傝傑偡丅夞楬恾偺堦晹丅

丂偙傟偼俉價僢僩偲係價僢僩偺僶僗暆曄姺偺惂屼夞楬偺堦晹偱丄儌僕儏乕儖柤偼乭FULL

MOON乭偱偡丅桼棃偼嵟嬤僥儗價偱

傗偭偰傞傾僯儊傜偟偄偱偡乮徫乯丅扨偵丄係價僢僩偺傾僋僙僗俀夞偱俉價僢僩偺僨乕僞偑傂偲偮懙偆偺偱丄敿寧傪俀偮崌傢偣偰枮寧

偩偲偄偄偨偄傜偟偄偱偡丅屻擔丒丒丒偙偺夞楬偼傕偭偲娙扨偵偱偒傑偟偨丅僔儞僾儖僀僘儀僗僩丅

仠幨恀偄傠偄傠

栚偵尒偊傞寢壥偑丄傗傞婥傪婲偙偝偣傞偲巚偭偰丄

傑偢偼價僨僆弌椡夞楬偐傜嶌傝巒傔傑偟偨丅

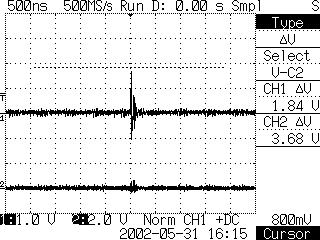

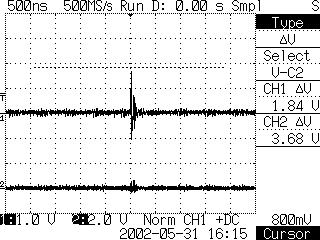

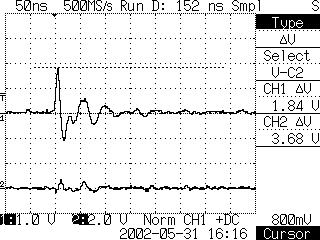

偙傟偼弶傔偰僥僗僩偟偨帪偺塮憸偱丄曄偱偡偹両 |

|

嵍偺彫偝偄婎斅偑杮懱偱偡丅

塃偺俁枃懕偒偺婎斅偼丄傓偐偟嶌偭偨僨傿僗僾儗僀僐儞僩儘乕儔

婎斅偱丄摨婜怣崋敪惗梡偲偟偰棙梡偟偰偄傑偡丅 |

|

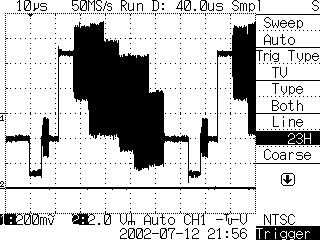

俵俙倃亄倫倢倳倱俬俬偱夞楬傪廋惓偟偨傜丄偡偖彂偒崬傫偱

寢壥偑妋偐傔傜傟傞偺偱曋棙偱偡丅 |

|

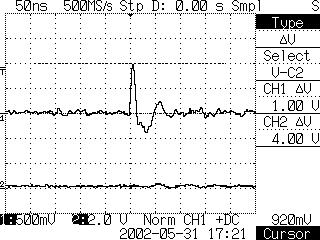

偳偆偵偐偙偆偵偐暥帤偑昞帵偝傟傑偟偨丅

偱傕傑偩僥僗僩抜奒偱偡丅 |

|

仠俀侽侽俀擭俆寧俁侾擔

丂婎杮揑偵摦偔傛偆偵側偭偨偑丄幚摦僥僗僩偵偍偄偰丄婲摦偐傜俀乣俁昩偱乽旘傫偱偟傑偆乿徢忬偑偁傝

偙偙悢擔偼尨場偑傢偐傜偢擸傫偱偄偨丅嵟弶偼惓忢側昞帵傪偡傞偗偳丄偡偖偵曵傟偰丄昞帵偑徚偊偨傝

壔偗暥帤偺梾楍偵側偭偰偟傑偆丅

丂儘僕僢僋傪壗搙傕壗搙傕尒捈偟偨偗偳丄栤戣側偄傛偆偩丅偆乕傫丄側偵偑僟儊側傫偩傠偆丒丒丒僾儘僕僃僋僩

偼丄峴偒媗傑偭偨丒丒丒乮揷岥僩儌儘儝晽乯丅

丂傑偝偐儂僗僩懁偺栤戣偠傖側偄傛側偁偲巚偄丄僆僔儘偱僞僀儈儞僌偺専徹傪偟偨丅僜乕僗僾儘僌儔儉傑偱

挷傋偰丄庤弴偵栤戣偑側偄偐傂偲偮傂偲偮妋偐傔偨丅栤戣側偄丅摉偨傝慜偩側丅儂僗僩懁偼姰惉昳側傫偩

偐傜丅

丂偲偙傠偑丒丒丒偦偺應掕拞偵婥偯偄偨帠偑偁偭偨丅惓忢偵摦偄偰傞両両

丂偳偆偄偆偙偲丠丠丂僴僢偲巚偭偨丅偦偆偩丄僲僀僘偐傕偟傟側偄丅抝偼丄棫偪忋偑偭偨丒丒丒乮揷岥僩儌儘儝晽乯丅

丂僆僔儘偑愙懕偝傟偰偄傞偲丄徢忬偑弌偢惓忢偵摦嶌偡傞丅偦偺怣崋偼僗僩儘乕僽偱丄壖偵僲僀僘偑擖傟偽

偱偨傜傔側僨乕僞傗僐儅儞僪偑憲傝崬傑傟傞帠偵側傞偩傠偆丅偩偐傜偙偺怣崋偵僲僀僘偑偺偭偰偄偰傕

僆僔儘偺僾儘乕僽偺梕検偱丄僲僀僘偑梷偊偙傑傟偰偄傞偐傜丄徢忬偑弌側偄傫偩傠偆丅

丂傓偐偟丄偡偱偵巗応偵弌夞偭偰偄偨惢昳偱丄偨傑偵僩儔僽儖傪婲偙偟偰栠偭偰偔傞搝偑偁偭偨丅偙傟偼帺暘偺

愝寁偠傖側偐偭偨偑丄偍傑偊僸儅偩傠偆偲偄偆帠偱丄挷嵏傪柦偠傜傟偰偄偨丅傑偩嬱偗弌偟偺帺暘偵偼傢偐傞

偼偢傕側偔丄嵟廔揑偵偼忋巌偑揙掙揑偵挷傋偰丄傗偭偲尨場傪偮偒偲傔偨偺偩偭偨丅

丂偦偺偲偒傕丄偲偁傞怣崋偵僆僔儘傪愙懕偟偰偄傞偲丄徢忬偑弌偢惓忢摦嶌偟偰偄偨丅傛偔挷傋傞偲丄僲僀僘偑

擖偭偰偄偨丅侾儃儖僩偖傜偄偺僸僎偑丅

丂傑偝偐僆僔儘傪偮側偄偩傑傑弌壸偡傞傢偗偵傕偄偐側偄偐傜乮傾儂偐乯丄俠俼僼傿儖僞傪晅偗丄懳嶔偟偨丅

愝寁揑側栤戣傕偁偭偨偲巚偆丅偦偺怣崋偺棫偪忋偑傝偱丄惂屼夞楬偑婲摦偡傞傛偆側曽幃偩偭偨偐傜丄

抁偄僷儖僗傕庴偗晅偗傞丄偮傑傝僲僀僘偵庛偄傢偗偩丅

丂傂偲偔偪偵僲僀僘偲偄偭偰傕丄尨場偼怓乆偁傞傫偩偗偳丄偦偺憰抲偺応崌偼丄僷僞乕儞偑挿偐偭偨偙偲丄

僋儘僢僋偲摨偠僶僢僼傽俬俠傪怣崋偑捠偭偰偒偰偄傞偙偲丄偁傞俴俽俬偐傜偺弌椡怣崋偦偺傕偺偵僌儔僂儞僪丒僶僂儞僗

偵傛傞僲僀僘偑偺偭偰偄偨偙偲偑尨場偩偭偨乮偦偺俴俽俬帺懱偺俧俶俢偑丄僷僢働乕僕僺儞悢係俉杮偵懳偟俀杮偟偐柍偔

庛偐偭偨偟丄僇僪偺僺儞側偺偱挿偐偭偨丅偙偺俴俽俬偑僶僗儅僗僞偵側偭偨帪偵丄懡悢偺僺儞傪嬱摦偡傞偨傔丄僌儔僂儞

僪丒僶僂儞僗偑敪惗偟傗偡偄乯丅

丂柺敀偄偺偼丄俿俿俴偺俀係係側傫偐丄偠偮偼夞楬偑係價僢僩偢偮俀僌儖乕僾偵側偭偰偄偰乮撪晹揑偵乯丄偦偺

僌儖乕僾撪偺怣崋偼偍屳偄偵塭嬁傪庴偗傗偡偄偑丄堘偆僌儖乕僾側傜塭嬁偑彫偝偐偭偨丅攇宍偑偦傟傪

徹柧偟偰偄偨丅挷嵏偟偰儗億乕僩傪採弌偟偨丅埲屻偺愝寁偵傕妶偐偟丄俀係係偺僺儞傾僒僀儞偵娭偟偰偼

摿偵婥傪晅偗丄婎斅愝寁埶棅帪偵偼丄偦偺巜帵傪偟偰偄偨丅

丂崱夞偺傗偮偼丄儂僗僩懁偲偺愙懕働乕僽儖偑俁侽僙儞僠傎偳偁傝丄偙偺挿偝偼婡婍偺惈幙忋傗傓傪摼側偄偑

傗偼傝俧俶俢偑庛偔丄僲僀僘偑忔傝傗偡偄孹岦偵偁傞丅

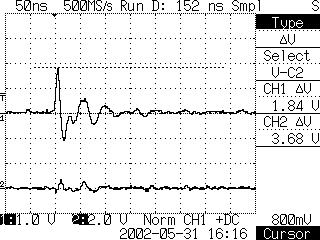

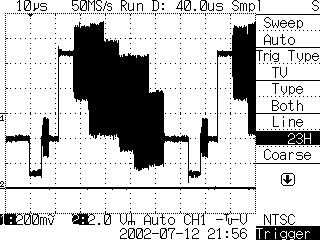

丂偙傟偑僗僩儘乕僽怣崋偵忔偭偨僲僀僘丅怣崋偼惓榑棟側偺偱丄捠忢俴偩丅俠俫俀偼娭學側偟丅

丂偙傟偼彮偟奼戝偟偰偁傞偐傜丄尒傟偽丄偁偁妋偐偵僲僀僘偩偹偊偲巚偆偩傠偆丅傆偩傫僨僕僞儖夞楬偩偐傜偲丄

俆倁乛俢俬倁偱尒偨傝偟偰偄傞偲丄側偐側偐婥偯偐側偄丅

丂偳偆傗偭偰偙偄偮傪偮偐傑偊傞偐偲偄偆偲丄俿俼俬俧丂俴俤倁俤俴傪彮偟偢偮壓偘偰偄偔丅偡傞偲丄偆傑偔僩儕僈偝傟偰

傂偭偐偗傜傟傞丅儘僕傾僫傪巊偆応崌傕丄僗儗僔儑儖僪儗儀儖傪挷惍偟偰偄偗偽丄偙偆傗偭偰傂偭偐偗傞帠偑偱偒傞丅

乮媡偵尵偆偲丄偦偆偄偆帠偑偱偒側偄儘僕傾僫偭偰杮奿揑偵巊偊側偄乯

丂偝偭偒偺攇宍傪丄傕偆偪傚偭偲奼戝偟偨傕偺丅

丂偙傟傪尒側偑傜丄僼傿儖僞偺掕悢傪寛傔傞傢偗偩偑丒丒丒傕偪傠傫怣崋偺抶墑傪嬌椡丄彫偝偔偡傞偙偲丅僨僕僞儖夞楬

偱傕僼傿儖僞傪幚尰偡傞偙偲偑偱偒傞偑丄俢僼儕僼儕偺暘偩偗抶墑偡傞偙偲傪峫椂偡傞丅

丂崱夞偺儘僕僢僋偱偼丄僗僩儘乕僽偺棫偪忋偑傝偑婎弨側偺偱丄偁傑傝抶傜偣偨偔側偄丅偩偐傜俠俼僼傿儖僞偵偟偨丅

丂偱丄偙傟偑挷惍拞偺攇宍丅偲傝偁偊偢侾儃儖僩埵傑偱梷偊偨傜栤戣側偄丅偙傟偐傜傕偆彮偟掕悢傪捛偄崬傫偱偄偔丅

丂偙傟偼巇條揑偵偱偒側偄偑丄僗僩儘乕僽偼晧榑棟偺傎偆偑丄僲僀僘儅乕僕儞揑偵桳棙偱偼丒丒丒丅

丂偝偰丄僲僀僘偺栤戣偼忔傝墇偊偨偐傜丄師偺僥乕儅偵偐偐傝傑偟傚偆偐偹丅

丂偙傟偼嶐栭偺幨恀偹丅偙偺帪偼丄尨場側傫偐慡偔傢偐傜側偐偭偨丅

仠俀侽侽俀擭俇寧俁擔

丂梉曽丄晹昳乮僩儕儅僐儞僨儞僒乯偑撏偄偨偺偱丄僎儞儘僢僋婎斅偑姰惉偱偒偨丅偱偒傞晹暘偼愭偵嶌偭偰偍偄偨偺偱丄

僩儕儅傪僴儞僟晅偗偡傞偩偗丅

丂僎儞儘僢僋偲偼丄悈暯摨婜怣崋偵摨婜偟偨僋儘僢僋傪嶌傞夞楬丅偙偙偱偼丄悈暯摨婜侾俆丏俈俁俲俫倸偐傜丄侾係丏俁侾俉侾俉

俵俫倸傪嶌傝弌偟偰偄傞丅偙傟傪僔僗僥儉僋儘僢僋偲偟偰僗乕僷乕僀儞億乕僘夞楬傪嬱摦偡傟偽丄僕僢僞偵傛傞悈暯曽岦偺

僊僓僊僓偑側偔側傞丅

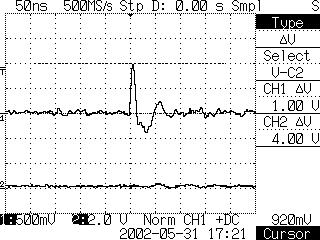

丂偙傟偑僎儞儘僢僋婎斅乮彫偝偔偰尒偊傫乯丅

丂僂僸儑丄傂傚偭偲偟偰偄偒側傝摦偔偐丠丂偲傝偁偊偢摦偐偟偰丄攇宍傪尒偰傒傛偆丅僷僞乕儞僕僃僱儗乕僞傪擖椡偵偮側偓

僎儞儘僢僋偺俠俴俲弌椡傪僆僔儘偱尒傞丅偍偍丄敪怳偼偟偰偄傞偑侾俀儊僈偖傜偄偩丒丒丒僩儕儅傪夞偟偰傒傞丒丒丒傛偟丄

侾係儊僈嬤曈偵崌傢偣傜傟傞側丅偲偙傠偑丒丒丒侾係丏俁侾俉侾俉俵俫倸偵崌傢偣傛偆偲帋傒傞偑丄偒傢偳偄丅僶僞僶僞曄摦偟偰

偄傞丅偙傝傖俹俴俴儘僢僋偟偰側偄側丅儘僢僋怣崋傪俠俫俀偵偮側偄偱娤應偟偰傒傞丅僶僞僶僞偩丅偁傝傖丅

丂側乕偵偑尨場側偺偐丒丒丒傑偢攝慄儈僗偼柍偐偭偨丅偦傟偠傖丄偁偲壗偩傠偆丅僲僀僘偐丠悈暯摨婜偺専弌偐傜偟偰

晄埨掕側姶怗傪摼偰偄偨丅

丂揹尮儔僀儞偺嫮壔傪幚巤偟偨丅傑偢僗僀僢僠儞僌揹尮偐傜奺婎斅傊偺攝慄傪丄懢偄傕偺偵岎姺丅奺婎斅偺揹尮擖椡偵

揹夝傪捛壛丅偲偔偵傾僫儘僌婎斅偵偼丄僙儔僐儞偲僐儌儞儌乕僪僼傿儖僞偲丄偱偐偄揹夝乮係俈侽儅僀僋儘乯傪捛壛丅偪傚偭偲

戝偘偝側姶偠傕偡傞偑丄儐僯僶乕僒儖婎斅偩偐傜偳偆偟偰傕揹尮傑傢傝偼昻庛側孹岦偵偁傝丄壜擻側尷傝偟偭偐傝偟偨

懳嶔傪偲傞丅

丂偦傟偐傜嵞搙傗偭偰傒偨傜丄偁傝傖丄慺捈偵儘僢僋偟偰偟傑偭偨丅婎杮揑偵埨掕偟偰偄傞丅

丂傑偩傑偩摴偺傝偼挿偄偑丄嵟屻偵偼僾儕儞僩婎斅壔偟偨偄丅傕偪傠傫丄帺傜僷僞乕儞愝寁偡傞丅偙傟偱傕婎斅愝寁偺

嫵堢傪庴偗婎斅俠俙俢傪埖偭偰偒偨丅偨偩偟壠偵偼俠俼俆侽侽侽側傫偐柍偄偐傜丄僼儕乕僜僼僩偺婎斅俠俙俢傪巊偆丅偒偭偲

抧崠傪尒傞偩傠偆乮徫乯丅

丂偦偆偄偊偽丄俻俥俹偺壓偵價傾傪懪偮側偲尵傢傟偨偭偗丅僨傿僢僾憛偵偐偗偨帪偵丄僴儞僟偑俻俥俹偺壓偵棳傟崬傓

壜擻惈偑偁傞偐傜偲尵傢傟偨丅

丂偦傟側傜丄惢憿巜帵偱俻俥俹偺棤懁偵儅僗僉儞僌僥乕僾傪揬傟偽偳偆偩偲丄惢憿宱尡幰偺巹偼尵偄偨偄偲偙傠偩偑丄

岥偛偨偊偡傞偲乽偍傑偊偼尓嫊偠傖側偄乿偲曉偝傟偰丄偁偁尵偊偽偙偆尵偆忬懺偵側傞偩傠偆丅儕僼儘乕偩偗偱丄僨傿僢僾

岺掱偼捠偝側偄偐傜娭學側偄応崌傕偁傞偱偟傚偲傕尵偄偨偄偲偙傠偩偑丅

丂偲偵偐偔婎杮偼丄俻俥俹偺壓偼儀僞傾乕僗偵偟傠偲丅暋嶨偵側偭偰偔傟偽偦偆傕尵偭偰傜傟側偄偐傜價傾偼懪偭偰椙偄

偲尵傢傟偨偐傜丄偦偆傗偭偰壽戣傪傗偭偮偗偰偄偨傜丄僟儊偩偲尵傢傟偰崲榝丅堦懱偳偆偡傟偽偄偄偺傗傜丄傢偐傜傫

偐傜壽戣曻婞偱僴僞儞乮徫乯丅

丂摉慠側偑傜丄晹昳柺俻俥俹偺壓偺儀僞傾乕僗傪丄偼傫偩柺偺傾乕僗偲偮側偖偨傔側傜丄價傾偼懪偭偰傕巟忈側偄丅偩偭偰

俧俶俢摨巑偮側偑偭偰傕娭學側偄傕傫偹丅

丂俢俬俹偩偭偨傜丄僺儞偺娫偵傕攝慄偑捠偣傞偐傜丄偗偭偙偆僷僞乕儞偑崿傫偱偄傞売強偵傕攝抲偱偒傞丅偲偙傠偑俻俥俹偼

姰慡偵捠偣傫傏偱偁傞丅僺儞娫側傫偐捠偣側偄丅

丂婎斅愝寁偺婎杮偲偟偰丄偨偲偊偽椉柺斅偺晹昳柺偺僷僞乕儞曽岦偼廲丄偼傫偩柺偼墶曽岦丄偺傛偆偵寛傑偭偰偄傞丅

俻俥俹偼晹昳柺偵攝抲偡傞偑丄僷僞乕儞偼廲偑婎杮偩偐傜丄墶曽岦傊偺堷偒弌偟偼嵟抁偵偟偰價傾傪懪偪丄偦偟偰

偼傫偩柺偱攝慄偡傞丅

丂偟偐偟俻俥俹偼丄晹昳柺偱峴偒愭偺晹昳傑偱僷僞乕儞偑堷偗偦偆偩偐傜丄廲墶偺婎杮傪柍帇偟偨偔側傞丅偦偙偑乽椪婡

墳曄乿偱乽廮擃側峫偊乿偱偁偭偰丄偦偺搒搙丄敾抐偟偰偄偔傕偺傜偟偄丅

丂傑偁婎斅愝寁偼丄堦擔拞僥儗價傪尒偰偄偰傕壗偲傕側偄恖偵偼岦偔偩傠偆丅巹偼僟儊偩偭偨丅偲偵偐偔挬偐傜栭拞傑偱

夋柺傪尒懕偗傞偺偱丄栚偑廩寣偟偰偟傑偆丅傛偔傗偭偰傜傟傞側偲巚偆丅

丂傆偩傫僷僜僐儞傪巊偭偰偄偰傕丄夋柺忋偱僪僉儏儊儞僩傪撉傒懕偗傞偺偼栚偑僔儑儃僔儑儃側偺偱丄偄偭偨傫巻偵弌偟偰

偐傜撉傫偱偄傞丅夞楬恾側傫偐偼巻偵弌偟偨傎偆偑椙偄丅夋柺偩偲晹暘偟偐尒偊側偄偑丄巻偵慡懱傪弌偡偲撉傒傗偡偄丅

丂偁偭丄僋儘僢僋偺僷僞乕儞偼僈乕僪偟傠偭偰尵傢傟偨偭偗丅俻俥俹偺僷僞乕儞偩偗偱庤堦攖側偺偵偄傑偝傜偳偆偟傠偭偰丅

僠僋僔儑乕儊丅僯儍儘儊乕丅傗偭傁傝丄婎斅愝寁偼乽埶棅偡傞懁乿偺傎偆偑妝偱偄偄傢丅僒儓僫儔乕丅

仠俀侽侽俀擭俇寧係擔

丂傑偩榑棟偺嶌傝崬傒偑娒偄晹暘傾儕丄僶僌偭偰偄偨丅偄傗丄僶僌偲偄偆傛傝姰惉偟偰側偐偭偨傫偩丅偁傑傝偵傕掅儗儀儖丅

丂傑偢崱挬偼丄僲乕僩偵乽崱擔偼丄偙偺栤戣傪夝寛偡傞両乿偲彂偄偰丄婥崌偄傪擖傟偨乮徫乯丅

丂傕偆丄嵟弶偺崰偵嶌偭偨晹暘側傫偐朰傟偐偗偰偄傞丅僲乕僩傪傔偔偭偰丄偍偝傜偄傪偟偨丅側傫偱僐僐丄偙偆側偭偰傫偩丠

偝偭傁傝傢偐傜傫丅帺暘偱嶌偭偨偺偵丄偦偺堄恾偡傞偲偙傠偑傢偐傜側偄丅帺暘偑傢偐傜側偗傟偽丄扤傕彆偗傛偆偑側偄丅

傕偭偲傕丄棅傟傞搝側傫偐偄側偄丅偠傖偁帺椡偱夝寛偡傞偟偐側偄丅偔偳偄丅

丂夞楬偺偙偲傪峫偊偰偄偨傜丄儊僔偺帠傑偱庤偑夞傜側偄丅拫偼丄拑榪堦攖偺儊僔偵攡姳偟侾屄丅偦傟偲僾儕儞偑侾屄偁偭偨

偺偱怘偭偨丅偦傟偩偗丅

丂偦偺屻丄墶偵側偭偰峫偊偰偄偨傜柊偔側傝丄婥偯偄偨傜屵屻俀帪偐丅偳偙偐尒抦傜偸搚抧傪偝傑傛偭偰偄偨柌偩偭偨丅

丂偦傟偐傜丄嵟弶偺崰偵昤偄偨僞僀儈儞僌僠儍乕僩傪偵傜傫偱偄偨傜丄媫偵摢偑傑傢傝偩偟丄乽偨傇傫偙偆偠傖偹乕偐乿偲

峫偊傪惍棟偡傋偔僲乕僩偵彂偒墸偭偨丅偙傟偱僗僢僉儕丅

丂儊僀儞僔乕働儞僒偺張棟偼係偮偺晹暘偐傜偱偒偰偄傞丅

丂昞帵梡偺儊儌儕偼忢偵撉傒弌偟偰丄夋柺偵昞帵偟側偗傟偽側傜側偄偺偱巭傔傜傟側偄丅儊儌儕偺撉傒彂偒偼丄儔儞僟儉

偵敪惗偡傞丅偩偐傜丄偙偺傛偆偵僞僀儈儞僌傪暘偗偰丄傾僋僙僗偑廳側傜側偄傛偆偵偟偰偄傞丅尒偐偗忋丄摨帪偵張棟偝傟偰

偄傞丅

丂棎朶側曽朄偼丄儊儌儕偺傾僪儗僗偲僨乕僞傪儅儖僠僾儗僋僒偱丄傾僋僙僗偺偁偭偨帪偺傒僽僠僢偲愗傝姺偊傞帠偩偑丄

偨傑偵側傜婥偵側傜側偄偑丄傾僋僙僗偺昿搙傗僞僀儈儞僌偵傛傝夋柺偵偪傜偮偒偑敪惗偡傞丅

丂係偮偺張棟丅

丂丂侾丏僥僉僗僩俼俙俵傪撉傒丄偦偺暥帤偵懳墳偡傞僉儍儔僕僃僱偺斣抧傪寛掕丅

丂丂俀丏僉儍儔僕僃僱偐傜暥帤僷僞乕儞傪廍偆丅

丂丂俁丏儊儌儕偐傜僶僢僼傽儗僕僗僞傊偺撉傒弌偟丅丂仸梫媮帪偺傒丅

丂丂係丏僶僢僼傽儗僕僗僞偐傜儊儌儕傊偺彂偒崬傒丅丂仸梫媮帪偺傒丅

丂偙偺偆偪嵟弶偺俀偮偲丄屻敿偺俀偮偲偱偼丄偁傞榑棟偑堎側傞晹暘偵婥偯偄偨丅偆乕傓丄峫偊偑懌傝側偐偭偨丅

丂偦偟偰丄偙偺廋惓偺榑棟傪捛壛偟偰僥僗僩偟偨偑丄側傫偐條巕偑偍偐偟偄丅傓傓偭丄側傫偐媡偩偧丒丒丒傕偆傂偲偮偺僠僢僾

偐傜偺怣崋偺榑棟偑媡偩偭偨丅偟傚乕傕側偄儈僗偩偭偨丅

丂偱丄夝寛偟偨偺偱丄栭偐傜怴偨側壽戣偵僠儍儗儞僕奐巒丅

丂偄傗丄乽師偼仜仜仜仜仜偵挧愴偡傞両乿傪彂偒捈偟偰丄乽師偼仜仜仜仜仜傪姰惉偡傞両両乿偵偟偨丅

丂偙傫側傆偆偵丅

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂傪姰惉偡傞両両

丂丂丂丂丂乽師偼仜仜仜仜仜偵挧愴偡傞両乿

仠俀侽侽俀擭俇寧俈擔

丂僎儞儘僢僋偼塸暥僨乕僞僔乕僩偟偐側偔偰丄乽僠僋僔儑僂丄婼抺暷塸傔丄撉傔側偄尵梩偱彂偔傫偠傖側偄両両乿偲搟傝嫸偭偰

偄偨偺偩偑丄偳偆偵偐偙偆偵偐丄抾憚愴朄偱堦抜棊偟偨(側傫傗偦傟乯丅

丂偮傑傝丄偲偔偵廳梫偦偆側晹暘偩偗廍偄撉傒偟偰丄僒儞僾儖夞楬恾捠傝偵丄偲傝偁偊偢嶌偭偰傒偨偺偱偁傞丅

丂傕偭偲傕丒丒丒嵟廔挷惍偱丄妋擣偑昁恵偩偑両両

丂偙偙俀乣俁擔偼丄怴偨側榑棟傪捛壛偟偰偄偨傜丄傑偲傕偵摦偐側偔側偭偰偟傑偄丄偲傫偱傕側偄揇徖偵懌傪偮偭偙傫偱丄

敳偗弌偣側偄傛偆側姶偠偩偭偨丅偙偙傑偱偒偰摦偐側偔側偭偨丅偳偆偟傛偆偭偰丅

丂偄偠偭偰偄偨傜傢偗偑傢偐傜側偔側傝丄偟傚偆偑側偔丄堦曕庤慜偺忬懺偵傑偱夞楬傪栠偟偨丅俀偮偺僠僢僾偑楢実偟偰

摦偄偰偄傞偺偱丄傑偢偳偪傜偵栤戣偑偁傞偺偐愗傝暘偗傪偟偰丄傂偲偮偢偮妋幚偵摦偔傛偆偵偟傛偆丅

丂僔儈儏儗乕僞偱挷傋傛偆偲巚偭偨偑丄愝掕偦偺懠偑柺搢偔偝偄丅帪娫偑偐偐傞偺偱丄偆偞偄丅偩偐傜捈愙丄尰応偵暦偙偆丅

惗偺僨乕僞傪帺暘偺栚偱尒傞偺偱偁傞丅偦傟偑堦斣憗偄丅

丂俴俤俢偲掞峈傪俉屄暲傋偨婎斅傪僕儍儞僋敔偐傜孈傝弌偟丄攝慄傪偮偗偨丅偦傟傪崱夞偺帋嶌婡偵愙懕丄僇僂儞僞抣偑僫儅偱

尒偊傞傛偆偵偟偨丅丒丒丒偦偟偨傜堦敪傛丄栤戣側偐偭偨丅偦傟偠傖傕偆堦曽偺愇偩側偲丅

丂傕偆堦曽偺愇偼丄偳偆尒偰傕娫堘偄側偄偲巚偭偰偄偨偺偩偑丄悢抣敾掕傪偟偰偄傞偲偙傠偱丄愙懕偑媡偩偭偨偨傔丄偆傑偔

摦偐側偐偭偨丅愙懕傪捈偟偨傜丄偡傫側傝摦偄偨丅側傫側傫偩偐丅

丂俵俙倃亄俹俴倀俽俬俬偺夞楬恾擖椡偱丄俈係俉俆偺弌椡偑傢偐傝偵偔偐偭偨偺傕尨場偩偲巚偆丅俙俴俛俷丄俙俤俛俷丄俙俧俛俷偲偄偆

昞婰偩偭偨丅傢偐傜傫丅俴偼懡暘俴倕倱倱偱丄乣傛傝彮側偄偲偄偆堄枴偩傠偆偗偳丄俙偲俛偺偳偭偪側傫偩偐丅俤偼僀僐乕儖偩傛

側偁丅俧偼俧倰倕倎倲倕倰偩傠偆丅傓偐偟俥俷俼俿俼俙俶偺俬俥暥偱丄丏俴俤丏偲偐丏俧俿丏偲偟偰偄偨偺傪巚偄弌偡丅俴俤偼丄俴倕倱倱丂俿倛倎値

倧倰丂俤倯倳倎倢偺棯偩偭偨偲巚偆丅

丂僜乕僗傪尒偰傕傛乕傢偐傜傫偐傜丄帋峴嶖岆偲偄偆偐丄偄偪偐偽偪偐偱丄愙懕傪媡偵偟偨傜偆傑偔偄偭偨丅

丂栭偵偼丄傛偆傗偔慡榑棟偺幚憰偑廔傢偭偨丅俀屄偺傾儖僥儔丄偳偭偪傕俋侽亾傑偱媗傔崬傫偩偑丄傑偩娒偄偐丅

丂僾儘偩偐傜丄乽偱偒偰摉慠乿側傫偩偗偳丄傗偭傁傝巇帠偺嬫愗傝偑偮偔偺偭偰丄偲偭偰傕婐偟偄両丂儚僢儂乕両両

丂傗偽偄両両丂揹婥岺帠偺昅婰帋尡丄崱搙偺擔梛偩傛丒丒丒搚梛偵堦婥偵偍偝傜偄傪偟側偄偲両両両両

仠俀侽侽俀擭俈寧俈擔

丂偮偄愭擔丄婎斅偑撏偄偨偽偐傝丅晹昳偼丄懙偭偰傞暘偐傜幚憰偟偨丅傑偩巆傝偺暘偑撏偐側偄丅偱傕憗偔摦偐偟偰傒偨偄

偐傜丄壗偲偐偦偺傊傫偵偁傞晹昳偱戙梡偟偰丄偲傝偁偊偢摦偔忬懺偵偟偨丅

丂僎僢丄側傫偐傢偐傜傫偑丄傾儖僥儔偑彂偗側偄丅栤戣敪惗両両

丂偄傗嵟弶偼彂偗偨偺偩偑丄摦偐側偄偺偱嵞搙彂偒崬傒傪帋傒偨傜丄彂偗側偐偭偨偺偩丅僄儔乕偑弌偰恑傑側偄丅崲偭偨丅

丂攝慄偵娫堘偄偑柍偄帠偼丄夞楬恾傪昤偄偨帪偵傕丄僶儔僢僋帋嶌偟偨帪偵傕丄傾乕僩儚乕僋帪偵傕妋擣偟偨丅偩偐傜娫堘偄

側偄丅嵟弶偺侾夞偼彂偗偨偺偩偐傜丅

仠俀侽侽俀擭俈寧侾俁擔

丂傆偭傆偭傆丅偮偄愭擔偐傜摦偄偰傞偧丅

丂傾儖僥儔偺彂偒崬傒偱僩儔僽偭偰丄僨僶僀僗傪壗屄傕徃揤偝偣偰偟傑偭偨丅彂偒崬傒偱儀儕僼傽僀僄儔乕偑弌偨傜丄傕偆師偺

弖娫偵偼堎忢偵擬偔側偭偰僽僠夡傟傞偺偩丒丒丒丅

丂俻俥俹儕儚乕僋僣乕儖乮擬晽婡乯偼柍偄偺偱丄僇僢僞乕偱懌傪愗偭偰庢傝奜偟丄僴儞僟媧偄庢傝慄偱僷僢僪傪偒傟偄偵偟偰丄

傾儖僐乕儖偱愻偭偰丄傑偨僴儞僟晅偗丄彂偒崬傒丄僄儔乕丄夁擬丄攋夡丄岎姺丄丒丒丒while(1)

丂俙偲俛偺偳偭偪偑夡傟偰偄傞偐丄俙偑擬偄偐傜夡傟偰偄傞傫偩傠偆偗偳丄傂傚偭偲偟偰俛傕夡傟偰偄偰埆偝傪偟偰偄傞偐傕

偟傟側偄丅偩偐傜俙偩偗岎姺偟偰傕僟儊偩傠偆丅傑偨夡傟傞偐傕偟傟側偄丅偆乕傫偳偆偟偨傜偄偄傫偩傠偆丅

丂偝偭偒拫怮偟偰偄偨傜媫偵揹榖偑柭傝丄柊偔偰挻僒僀傾僋僶僢僪僐儞僨傿僔儑儞丄俽俬俶俹俷僐乕僪偱尵偊偽侾侾侾侾侾偐丅

丂崱夞偺婎斅偼丄俀偮偺傾儖僥儔偑偍屳偄偵偮側偑偭偰偄傞偐傜丄偳偪傜偐偑偍偐偟偔側偭偰丄弌椡摨巑偑偮側偑傞傛偆側

帠偵側傟偽丄僨僶僀僗偑攋夡偝傟偰偟傑偆丅栵夘側帠偩丅

丂婎斅専恾偼娫堘偄側偐偭偨偺偩偑丄偄傗丄傕偟偐偟偰娫堘偄偑偁傞偐傕偟傟側偄偲巚偭偰丄傑偨僷僞乕儞傪侾杮偢偮偨偳偭偰

慡晹妋偐傔偨丅娫堘偄偼丄側偐偭偨丅僾儘僕僃僋僩偼丄峴偒媗傑偭偨丒丒丒乮揷岥僩儌儘儝晽乯丅

丂彂偒崬傒偺俰俿俙俧怣崋傪僆僔儘偱尒傛偆偵傕丄嵟弶偐傜僄儔乕偑弌偰恑傔側偄丅僨乕僞偑偳偙偱壔偗偰傞偺偐扵偣側偄丅

嵟弶偪傚傃偭偲弌傞怣崋傪僩儕僈偱傂偭偐偗偰尒偰丄偆乕傫偍偐偟偔側偄傫偩偑側偁偲丄偦傫側挷巕丅偙傫側偙偲丄偄偮傑偱

傗偭偰偄偰傕傜偪偁偐傫偹傫丅

丂嵟弶偵僆僔儘偱尒偨偲偒偼丄僴僢偲婥偯偄偨帠偑偁偭偨偹丅傾儖僥儔偺僨乕僞僔乕僩偵丄俰俿俙俧彂偒崬傒夞楬偺椺偑偁偭偰

乽偙偺捠傝偵嶌傟偽傑偢娫堘偄側偄偩傠偆乿偲巚偆傛偹丄晛捠丅偦傟偑僟儊側傫偩丅僾儖傾僢僾侾僉儘偠傖丄俴儗儀儖偑晜偄偰偟

傑偆傛両丂偦傟偼幚嵺偵僆僔儘偱尒傞傑偱巚偄傕偟側偐偭偨丅夞楬椺偑偁傞傫偩偐傜偦偺捠傝偵嶌傞傕傫偩偲巚偭偰偄偨丅

丂傑偨傾儊岞偵傗傜傟偰偟傑偭偨丅

丂俙偲俛偺僠僢僾傪巜偱偝傢偭偰傒偰丄堎忢偵擬偄曽偑夡傟偰偄傞偲敾抐偟偰丄偲傝偼偢偟偨丅俙偑夡傟偰偄傞傛偆偩偭偨丅

俛偩偗傪扨撈偱摦偐偟偰傒偨丅偁偭摦偄偰傞傛丒丒丒丅夋柺昞帵梡偺僠僢僾偩偐傜丄寢壥偑梕堈偵妋擣偱偒偰彆偐偭偨丅

丂偟偐偟偩丄偙偺俛偑棤愗傝幰偭偰帠傕峫偊傜傟傞丅俙偺弌椡僺儞偵懳偟偰丄惗堄婥偵傕俛偐傜弌椡偟偰偄傞乮堎忢乯傛偆側

僺儞偼柍偄偐丄侾僺儞偢偮偟偮偙偔挷傋偨丅俙傪彍嫀偟偨屻偺僷僞乕儞偵僆僔儘傪摉偰偰丄俙偺弌椡僺儞偵俛偐傜怣崋偑

棃偰偄側偄偐妋偐傔偨丅偨偲偊偽僆乕僾儞側傜巜偱傆傟偰傒傞偲傢偐傞丅偦偆傗偭偰栚偲庤偲幏擮偱慡晹妋偐傔偨丅栤戣偼

側偐偭偨丅

丂偙傟側傜丄俙傪幚憰偟偰傕堦墳戝忎晇偩丅偁偲偼彂偒崬傒偑偆傑偔偄偔偐偳偆偐偑彑晧偩丅

丂嵟弶偐傜儚儞僠僢僾偵偟偰偍偗偽丄僷僞乕儞傕娙扨偩偭偨偟丄偙傫側栤戣傕柍偐偭偨傫偠傖側偄偐丅偄傗丄庤帩偪晹昳偩偗偱

壗偲偐挧愴偟偰傒傛偆偲偄偆帠偩偭偨偐傜丄偙傟偼偙傟偱偄偄傫偩丅

丂傾儖僥儔偺僇僞儘僌偺昞巻偩偭偨偐朰傟偨偑丄婎斅忋偺僨僶僀僗偑慡偰傾儖僥儔偵側偭偰偄傞偺偑偁偭偨丅偙傫側婎斅傕

捒偟偄傕傫偩乮儎僀丄侾屄偖傜偄僓僀儕儞僋僗偺偣傠乯丅

丂偙傫側傆偆偵丄暋悢偺僨僶僀僗傪偮側偄偱丄彂偒崬傒傪偡傞帠傕偁傞偼偢偩丅偩偐傜丄偱偒側偒傖偍偐偟偄傫偩傛偹丅偄傑丄

偙偺栤戣傪崕暈偟偰偍偐側偗傟偽丄彨棃偦傫側婎斅傪傗傞帪偵傑偨僴儅偭偰偟傑偆偐傕偟傟側偄丅

丂偠偮偼丄偙偺栤戣偼儐僯僶乕僒儖婎斅偱嶌偭偰偄偨崰丄偡偱偵婥偯偄偰偄偨丅偩偗偳偦偺帪偼丄偙傫側僌僠儍僌僠儍偺婎斅

偱丄偟偐傕俙偲俛偺娫傪僼儔僢僩働乕僽儖偱偺偽偟偰傞偐傜丄彂偒崬傒僄儔乕偡傞傫偩傠偆偲巚偄偙傒丄怺偔挷傋側偐偭偨丅偙傟偑

傑偢偐偭偨丅傕偭偲捛媶偟側偗傟偽側傜側偐偭偨丅傕偭偲傕偭偲尰幚傪尒傟偽傛偐偭偨丅怺偔斀徣丅

丂俰俿俙俧偺攝慄側傫偐丄儅僯儏傾儖捠傝偩傠偲偟偐巚傢側偐偭偨傕傫偹丅娒偄両両

丂寢嬊丄俛偑惗偒偰偄偨偺偱丄俙偩偗扨撈偱彂偒崬傒偑偱偒傞傛偆偵丄僷僞乕儞僇僢僩仌僕儍儞僷乕慄偱廋惓偟丄俙偺彂偒崬傒偼

惉岟偟偨丅

丂僠僋僔儑乕儊丄偁偺傾儖僥儔偺昞巻偺丄傾儖僥儔偩傜偗偺婎斅偼僂僜偩傠丅彂偒崬傒僄儔乕偟偰丄弌椡摨巑偑徴撍偟偨傜丄

僨僶僀僗偑僀僇儗偰丄壗偑壗偩偐傢偗傢偐傫側偔側傞偧両両丂偁傜偐偠傔彂偒崬傒傪偟偰偐傜幚憰偣偵傖側傜傫丅偦傟偠傖

俬俽俹偠傖側偄偭偰丒丒丒丅

丂僙儈僫乕偵偼壗搙偐峴偭偨偙偲偑偁傞偑丄懠幮偲斾妑偱偺桪埵惈偲偐愰揱丄嵟怴媄弍偺俹俼偽偐傝偠傖側偔偰丄偙偆偄偆丄

偳傠偔偝偄悽奅傕傗偭偰傎偟偄丅儌僲偑摦偗偽丄怓婥傪弌偟偰嵟怴媄弍偲偐巊偭偰傗偭偰傕椙偄偑丄儌僲偑摦偐側偗傟偽

壗偵傕側傜側偄両両

丂偙傟偐傜怴偟偔摫擖偡傞恖偺偨傔偺丄婎慴傪傗傞帪娫傕愝偗偰傎偟偄傕傫偩側丅

丂偟偐偟嬤擭偼丄攷懡偱偺僙儈僫乕偼柍偄傒偨偄丅偆乕傓丅埲慜傕丄戙棟揦側偳偐傜丄嶲壛恖悢傪偐偒廤傔傞偺偑戝曄偲偐

偩偭偨偺偩偑丅嬨廈偼彮側偄偺偱戝曄側傫偩側丅

丂偦偆偄偊偽僓僀儕儞僋僗偺僨僶僀僗偱傕彂偒崬傒僩儔僽儖偼宱尡偟偨偧丅傕偆偢偄傇傫慜丅

丂偁偺偲偒偼丄俬俽俹働乕僽儖偠傖側偔偰丄僔儕傾儖俼俷俵偩偭偨傫偩偑丄怴偟偄帋嶌婡偑慡偔摦偐側偐偭偨傢偗偩丅偘偘乕傫丅

偳偆偟傛偆丄媷抧偵捛偄偮傔傜傟偨乮揷岥僩儌儘儝晽乯丅

丂偨偟偐僔儕傾儖俼俷俵僄儈儏儗乕僞偱偼摦偄偨傫偩傛側丅偟傚偆偑側偄偐傜丄偙傟傪僽儔乕儞偲丄晅懏昳偱晅偗傞偐偭偰丄傪偄傪偄丅

丂僔儕傾儖俼俷俵僄儈儏儗乕僞偼丄偄傑偱偙偦巗斕偝傟偰偄傞偑丄摉帪偼俿俿俴偲憢晅偒俤俹俼俷俵傪慻傒崌傢偣偰帺嶌偟偨傕偺

傪巊偭偰偄偨丅彜攧偵側傞傫側傜丄偁偺偲偒偵攧傝弌偟偰偍偔傫偩偭偨傛丅

丂俷俿俹偺僔儕傾儖俼俷俵傪巊偭偰偄偨傜丄廋惓偺偨傃偵僑儈偵側偭偰傕偭偨偄側偄偐傜側丅偦偆偄偆僯乕僘偑偁偭偨傢偗偩丅

丂寢嬊丄儊乕僇偵暦偄偨傜丄乽僐儞僨儞僒偮偗偰偔偩偝偄乿偲偄偆夞摎偱丄揹榖偱壗僺儞偵偳偺偔傜偄偺梕検偺僐儞僨儞僒傪偮偗傞

偺偐嫵偊偰傕傜偭偰丄偦偺捠傝偵偟偨傜摦偄偨傛丒丒丒丅

丂偦傟偱傕怱攝偱丄忋巌偐傜丄乽偍傑偊丄侾侽侽侽夞偖傜偄揹尮俷俶乛俷俥俥僒僀僋儖偟傠傛乿偲丄傂偨偡傜庤摦偱丄僗僀僢僠傪憖嶌偟

懕偗偰妋擣偟偨妎偊偑偁傞丅

丂榖偼曄傢傞偺偩偑丄曮偺帩偪晠傟丅

丂價僨僆怣崋傪娤應偡傞偨傔偵丄偄傢備傞乽儔僀儞僙儗僋僞乕乿偲偄偆儌僲偑昁梫偩偲姶偠偰偄偨丅摿掕偺憱嵏慄偺攇宍偺傒傪

尒傞帠偑偱偒傞偺偩丅摿掕偺憱嵏慄偺攇宍偺傒傪尒傞昁梫偑偁傞丅僗乕僷乕僀儞億乕僘晹暘偺傒尒傛偆偲巚偭偰傕丄儔僀儞

僙儗僋僞乕偑柍偐偭偨傜柍棟偩傕傫偹丅

丂彂愋傗倂倕倐偱丄偄傠傫側惢嶌椺傪尒偰偄偨偑丄偆乕傓丄杮懱偺僨僶僢僌偑戝曄側偺偵偙傫側偺嶌偭偰傞僸儅偹乕傛丅

丂偲傝偁偊偢丄侾侽侽俬俼俤僼儖僇儔乕僶乕乮廲幦側偺偱傎偲傫偳慡晹偺憱嵏慄偑摨偠偱偟傚偆乯傪棙梡偟偰丄攇宍傪娤應偟偰偄偨丅

偦偆偄偊偽丄僥儗價梡偺僩儕僈愝掕偼柍偐偭偨偐側偁偲丄偄傠偄傠偄偠偔偭偰偄偨傜丄俴倝値倕偲偄偆崁栚傪敪尒丅

丂側傫偩傠俴倝値倕偭偰丒丒丒俙俠揹尮儔僀儞偵摨婜偟偨傗偮偐丠側偳偲僩儃働偰偄偨丅俥倀俶俠俿俬俷俶僣儅儈傪夞偡偲丄偙偺悢帤偑

曄壔偡傞丅偦傟偵崌傢偣偰丄攇宍偑侾屄偢偮僘儗傞丅

丂傓傓偭丒丒丒丄偙傟偭偰傕偟偐偟偰丄儔僀儞僙儗僋僞乕丠乮徫乯

丂偛傔傫娾捠偝傫両両

丂偙偺僆僔儘俁擭偖傜偄巊偭偰偄傞偗偳丄偙傫側曋棙側婡擻傪擖傟偰偔傟偰偄偨偺偵丄偄傑傑偱婥偯偐側偐偭偨傛両両

丂偙傟偠傖偁丄儊乕僇乕偺恖偨偪偵怽偟栿側偄丅曋棙側婡擻偵婥偯偄偨偺偱丄崱擔偐傜偼妶梡偟偰偄偙偆丅

丂傑偝偵丄偄傑傑偱曮偺帩偪晠傟偩偭偨両両

戝儃働偼丄偍慜揷両両

丂屄恖揑偵偼僥僋僩儘偺傎偆偑偄偄偐側偲巚偆傫偩偑丄偙傟傪攦偭偨摉帪偼娾捠偺俛俼俬俶俧俷乮俢俽亅俉俉侾俀乯偺傎偆偑埨偐偭偨

偟丄僾儕儞僞傗僼儘僢僺乕傕昗弨憰旛偩偭偨偐傜慖傫偩丅

丂傂偲偮晄枮傪尵偊偽丄擖椡抂巕偑愨墢偝傟偰偄側偄偐傜丄揹榖夞慄偺怣崋傪尒傞偲偒偵僴儉偑擖傞帠傗偹丅撪晹偺僗僀僢僠儞僌

揹尮偐丄儔僀儞僼傿儖僞偺偲偙傠偱僔儍乕僔俧俶俢偲偮側偑偭偰傞傫偩傠偆丅揹榖夞慄偺娤應帪偵偼丄愨墢僩儔儞僗偑昁梫偠傖傫丅

偁偺僥僋僩儘偺丄揹抮偱摦偔傗偮丄偁傟偑揹榖夞慄梡偵偼僺僢僞儕側傫偩偑側偁丅

仠俀侽侽俀擭俋寧侾俋擔丂曐棷

乽傂傒偮俁乿偑峴偒媗傑偭偨丅

丂偁偲堦曕偱姰惉偩偭偨偑丄偙偺堦曕偼戝偒偔丄怺偡偓傞堦曕偩偭偨丅

丂楢擔楢栭偺捛媶偺枛丄僎儞儘僢僋偺弌椡廃攇悢偺栤戣偩偲偄偆帠偑傢偐偭偨丅

丂僲儞僀儞僞儗乕僗擖椡偱偼廃攇悢傕昞帵傕惓偟偐偭偨丅

丂偩偑僀儞僞儗乕僗偱偼丄廃攇悢偑崅傔偵側傝丄暥帤偑僊僓僊僓偵側偭偨丅

丂抝偼丄栤戣売強偺愗傝暘偗傪偟偨丅

丂偳偪傜偺夞楬偑栤戣側偺偐丄挷傋恠偔偟偨丅

丂悈暯摨婜傪傆偨偮偺夞楬偑巊偭偰偄偨丅

丂傂偲偮偼僎儞儘僢僋丄傕偆傂偲偮偼乮悈暯悅捈乯僞僀儈儞僌夞楬偩偭偨丅

丂僲儞僀儞僞儗乕僗擖椡偱偼惓忢偩偐傜丄僞僀儈儞僌夞楬偼栤戣側偐偭偨丅

丂僎儞儘僢僋偩丅

丂僀儞僞儗乕僗偲僲儞僀儞僞儗乕僗擖椡偱寢壥偑堎側傞丅

丂偦偆偩丅偦偺堘偄偼丄愗傝崬傒僷儖僗偐丅侾乛俀俫偺僘儗偐丅

丂攇宍傪尒側偑傜丄偄偔偮傕偺夞楬傪帋偟偨丅

丂偟偐偟丄偙偲偛偲偔攕傟嫀偭偨丅

丂抝偼丄偁偒傜傔側偐偭偨丅

丂乽偙傟偼丄帺暘偺椡偱側傫偲偐側傞悽奅偩丅愨懳側傫偲偐側傞丅偁偒傜傔側偄丅乿

丂帺傜傪椼傑偟懕偗偨丅

丂戝嬥傪偼偨偄偰丄儘僕傾僫傪攦偭偨丅

丂傕偆屻栠傝偼偱偒側偐偭偨丅

丂帺傜傪惛恄揑偵捛偄崬傫偩丅攚悈偺恮偩偭偨丅

丂寠偑偁偔傎偳攇宍傪偵傜傒丄偄偔偮傕偺壖愢傪偨偰丄夞楬傪慻傫偩丅

丂偟偐偟丄栤戣揰偼堦岦偵夵慞偟側偐偭偨丅

丂僾儘僕僃僋僩偼丄峴偒媗傑偭偨丅

丂丒丒丒丒丒丒戝曄丄庛偭偰偄傑偡丅側傫偱偆傑偔偄偐側偄偺偐傢偐傝傑偣傫丅

偄傑峫偊傜傟傞偡傋偰偺庤偼恠偔偟傑偟偨丅

丂偙傫側擄偟偄榖丄憡択偱偒傞憡庤偼廃埻偵偄傑偣傫丅

丂榑棟偐傜婎斅傑偱慡晹傂偲傝偱傗偭偰偒偨偺偵丄姰惉傑偱偺偁偲堦曕偑丄

偳偆偟偰傕丄偳偆偟偰傕丄恑傔傑偣傫丅

丂懌傪昁巰偱摦偐偟偰偄傞偺偵丄偪偭偲傕慜偵恑傑側偄柌傪尒傞偖傜偄偱偡丅

丂崲傝傑偟偨丅

丂偙傟埲忋偙偩傢偭偰丄懕偗偰偄偰傕帪娫偽偐傝偑夁偓偦偆偱偡丅

仠俀侽侽俀擭侾俀寧係擔

丂傆偭傆偭傆丅傑偩丄偁偒傜傔偰偄側偄偺偠傖丅

丂

栠傞